AI News

17 Mar 2026

Read 10 min

How to use AI chiplet design software to cut costs

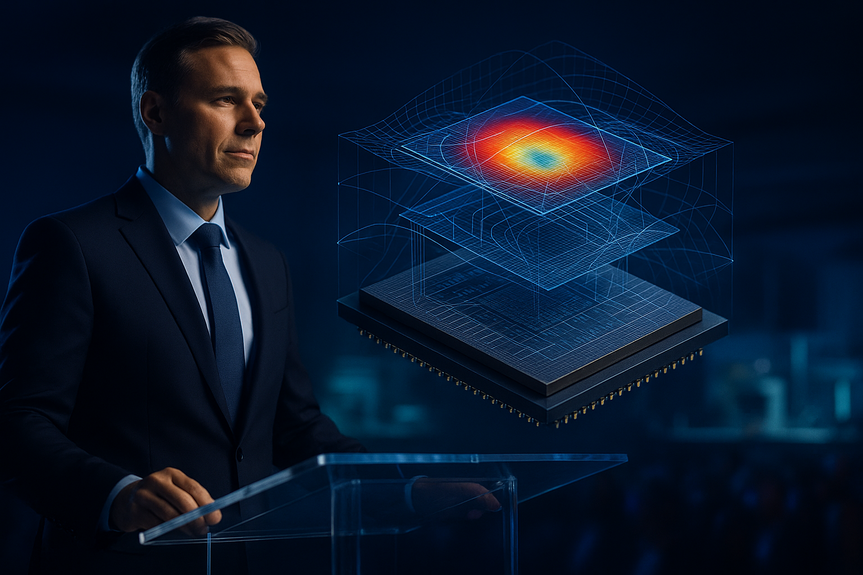

AI chiplet design software helps engineers integrate thermal and mechanical checks to reduce cost.

Why chiplets change the cost equation

From one big die to many small ones

– One large die is hard to yield and can be very expensive at leading nodes. – Several chiplets let you mix process nodes and reuse IP. – The package becomes part of system performance, not just a container.New risks that hit your budget

– Heat can cause parts to warp and break bonds between chiplets. – Power density rises; hotspots can limit clock targets. – Long interconnects add latency and power. – Late fixes mean extra masks, new substrates, and schedule slips. This is why design teams now need electrical, thermal, and mechanical analysis up front, not at the end.How AI chiplet design software saves money

Bring physics into the design phase

– Co-simulate power, temperature, stress, and signal integrity while you floorplan. – See how package materials and stack height affect warpage before layout freezes. – Choose bump maps, TSVs, and spacers with real data, not guesswork.Automate multi-die floorplanning and interconnects

– Optimize die partitioning to reduce long links and power-hungry SerDes. – Place compute near memory chiplets to cut latency and cooling load. – Validate bandwidth and timing across dies with package parasitics included.Measure cost, performance, and power together

– Compare process-node mixes (e.g., logic on advanced, I/O on mature) with live cost models. – Trade off substrate layers, cooling options, and die sizes to hit a bill of materials target. – Lock decisions sooner with evidence, reducing redesigns.Step-by-step: Cut costs without losing performance

1) Set system targets clearly

– Define power, performance, area, and cost goals. – Add thermal and reliability limits (junction temp, warpage, fatigue cycles).2) Partition with early multi-physics models

– Try several chiplet splits and package options. – Score each option on PPA, thermals, and total cost.3) Co-optimize packaging and dies

– Select substrates, underfill, and heatsinks with the model in the loop. – Adjust bump pitch, die thickness, and stack order to reduce stress.4) Close power and timing with package parasitics

– Include interposer and RDL models in signoff. – Confirm timing budgets with cross-die latency and skew.5) Validate manufacturability

– Run DRC/DFM across dies and package. – Check assembly tolerances and test access early.6) Plan for test and yield

– Insert DFT for each die and for die-to-die links. – Use redundancy and repair to boost yield where it matters most.7) Use silicon feedback to refine models

– Feed real thermal maps and stress data back into design rules. – Improve forecasts for the next generation.What savings can teams expect?

– Fewer re-spins: Catching thermal or packaging issues early can avoid one or more re-spins, saving months and significant mask and assembly costs. – Better yield: Smaller chiplets often yield better than one large die, reducing scrap and improving usable output. – Right-sized nodes: Put advanced logic on leading nodes and keep analog or I/O on mature nodes to cut wafer cost. – Lower cooling overhead: Balanced thermal design can reduce heatsink and system cooling spend. – Tighter schedules: Integrated flows remove handoffs and rework, which reduces program risk. Real results vary by product, but teams commonly see faster convergence, fewer late issues, and a lower bill of materials when they use integrated co-design.Toolchain checklist for multi-die success

– Unified design cockpit for logic, package, and system views – Thermal, mechanical stress, and CFD analysis tied to layout – Power integrity and signal integrity with package parasitics – Automated multi-die floorplanning and die-to-die link synthesis – Support for chiplet standards (e.g., UCIe) and custom links – Cost modeling for wafers, substrates, assembly, and cooling – DRC/DFM across dies and advanced packaging – Silicon lifecycle management to loop back measurementsCommon pitfalls and how to avoid them

– Siloed teams: Break silos. Share one model of the system and its package. – Late thermal analysis: Run thermal and stress checks at concept, not after layout. – Over-optimizing a single die: Optimize across dies and the package, not in isolation. – Ignoring package parasitics: Include them in timing and PI/SI signoff. – Weak test strategy: Plan DFT and die-to-die test paths early to protect yield. – No cost lens: Track cost impact with every design change.A note on today’s tools

Synopsys’ latest suite, strengthened by Ansys technology, targets this exact workflow. It blends chip design, packaging, and physics into one process. The goal is simple: decide earlier, verify faster, and reduce surprises that drive up cost near tape-out. Smart teams do not wait for late-stage fails. They design with physics and packaging from day one. With the right AI chiplet design software, you can hit performance and power goals while cutting cost and risk.For more news: Click Here

FAQ

Contents